因为专业

所以领先

人工智能、AI芯片算力、汽车电子这三个领域对封装技术的要求各有侧重,因此采用的工艺也有明显差异。下面我将分别详细阐述。

| 领域 | 核心需求 | 关键封装技术工艺 |

| 人工智能 (终端侧AI) | 尺寸微型化、功耗低、成本可控 | WLCSP, Fan-In/Out WLP, SiP |

| AI芯片算力 (云端/训练) | 超高算力、极高带宽、巨大功耗管理 | 2.5D/3D IC (CoWoS, HBM), Chiplets, TCB |

| 汽车电子 | 超高可靠性、耐高温/振动、长寿命 | QFN, AEC-Q100认证的WLCSP/FOWLP, SiP, 功率模块封装 |

这个领域主要指部署在手机、智能音箱、摄像头、AR/VR设备等终端设备上的AI加速芯片。它们通常用于执行轻量级的推理任务。

核心挑战:

尺寸限制:设备内部空间极其有限。

功耗限制:需要长续航,发热必须可控。

成本压力:面向消费电子市场,成本敏感。

主要封装技术:

描述:将处理器、存储器、无源元件(电阻、电容)等多个不同类型的芯片和组件,通过高密度基板或嵌入式方式集成在一个封装体内,形成一个功能完整的系统。

优势:极大缩短互连长度,提升系统性能,减小整体模块体积。

应用:可穿戴设备、物联网模块中的AI功能集成。

扇入型 (Fan-In):是WLCSP的基础,引脚都在芯片面积内。当芯片I/O数量不多时使用。

扇出型 (Fan-Out WLP):当芯片I/O数量增加,芯片面积内无法容纳所有引脚时,将芯片嵌入到环氧模塑料中,然后在“重构的晶圆”上重新分布线路,将引脚“扇出”到芯片实体面积之外。

优势:在保持小尺寸的同时,实现了更高的I/O密度和更好的散热。Fan-Out 技术非常关键,因为它允许集成多个芯片。

应用:苹果A系列处理器、高通骁龙芯片等广泛采用。

描述:直接在晶圆上进行封装和植球,完成后切割下来的芯片尺寸几乎与裸芯片相同。这是目前最主流的微型化封装技术之一。

优势:尺寸极小、电性能好(引线短)、成本低。

应用:手机中的NPU、图像信号处理器等。

晶圆级芯片尺寸封装 (WLCSP)

扇入型/扇出型晶圆级封装 (Fan-In/Fan-Out WLP)

系统级封装 (SiP)

这个领域指用于数据中心、超算等进行AI模型训练和大规模推理的芯片,如NVIDIA的GPU、Google的TPU等。

核心挑战:

性能瓶颈:需要突破“内存墙”(内存速度跟不上计算速度)。

互连带宽:需要极高的芯片间通信带宽。

热管理:功耗动辄数百瓦,散热是巨大挑战。

主要封装技术:

描述:一种用于3D堆叠的精密键合技术,能实现更小的凸点间距和更高的连接可靠性,对散热也至关重要。

应用:高端3D堆叠封装的关键工艺。

描述:将一颗大芯片分解成多个更小、功能更单一的“小芯片”,然后通过2.5D或3D技术集成在一起。芯片间采用超高密度互连标准,如UCIe。

优势:提升大芯片良率、降低成本、实现“异构集成”(不同工艺节点的芯片可以组合)。

应用:AMD的EPYC处理器是成功案例,AI芯片也广泛采用此理念。

描述:HBM本身就是3D封装的典范,它将多个DRAM芯片堆叠在一起,并通过TSV与底层的逻辑芯片(GPU)连接。HBM与计算芯片的集成必须依赖2.5D中介层技术。

优势:提供远超GDDR的带宽。

描述:这是该领域的核心技术。

优势:彻底解决了高带宽内存接入问题,极大提升了系统性能和能效。

应用:所有高端AI训练芯片(NVIDIA H100/GH200, AMD MI300等)都采用2.5D集成HBM。

2.5D:将多个芯片(如GPU核心和HBM)并排放在一个硅中介层 上。中介层内部有高密度的硅通孔,提供芯片间超高速互连,再通过中介层下方的焊球连接到PCB上。NVIDIA的CoWoS 是其中最著名的技术。

3D:将芯片像盖楼一样垂直堆叠,通过硅通孔 直接连接。这提供了最高的互连密度和带宽。

2.5D/3D 集成封装

高带宽内存 (HBM) 的集成

Chiplets (小芯片) 与先进互连

热压键合 (TCB)

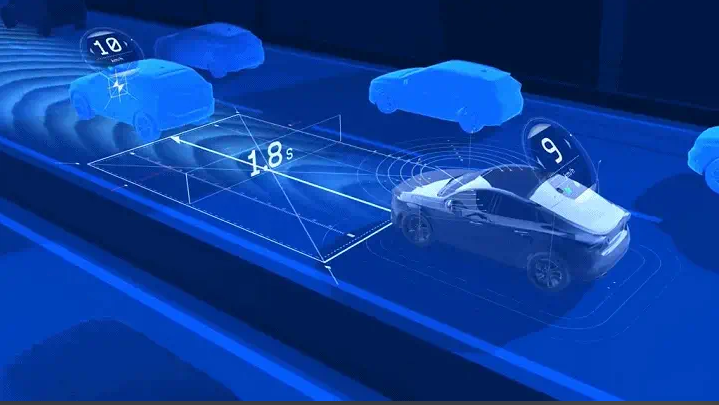

汽车电子涵盖范围很广,从信息娱乐系统到最关键的动力总成、ADAS(高级驾驶辅助系统)。这里主要讨论涉及计算和功率控制的电子部分。

核心挑战:

极端可靠性:必须保证在-40°C到125°C甚至更高的温度范围、高振动、高湿度环境下工作15年以上。

零缺陷要求:尤其是安全相关部件,故障率要求极低。

大功率处理:电动汽车需要处理高电压、大电流。

主要封装技术:

描述:专门用于处理高功率的封装技术,如电动汽车的逆变器中的IGBT和SiC(碳化硅)模块。

技术:采用直接覆铜基板、银烧结 等工艺,确保在高电压、大电流和高温下的稳定运行。

趋势:从焊接转向烧结,从硅基转向碳化硅/氮化镓,封装技术是关键使能因素。

描述:与消费电子类似,但可靠性要求是天壤之别。用于将ADAS域控制器中的多种芯片(如处理器、存储器、电源管理芯片)集成在一个高可靠性的封装内。

优势:减少PCB上的元件数量,提升系统可靠性和抗振动能力。

描述:许多封装形式本身与消费电子相同,但必须通过AEC-Q100等车规级可靠性认证。这意味着材料、工艺控制和测试标准都严格得多。

类型:QFN、LQFP 等因其良好的散热和可靠性,在MCU、传感器中广泛应用。车规级的 WLCSP 和 FOWLP 也用于ADAS摄像头中的图像处理器等。

符合车规认证的标准封装

系统级封装 (SiP)

功率模块封装

人工智能(终端) 追求 “小而省”,技术核心是 WLP 和 SiP,在有限空间内实现足够算力。

AI芯片算力(云端) 追求 “大而快”,技术核心是 2.5D/3D 和 Chiplets,不惜成本突破性能和带宽极限。

汽车电子 追求 “稳而强”,技术核心是 车规级认证 和 高可靠性设计,在保证万无一失的前提下,逐步引入先进集成和功率封装技术。

水基清洗的工艺和设备配置选择对清洗精密器件尤其重要,一旦选定,就会作为一个长期的使用和运行方式。水基清洗剂必须满足清洗、漂洗、干燥的全工艺流程。

污染物有多种,可归纳为离子型和非离子型两大类。离子型污染物接触到环境中的湿气,通电后发生电化学迁移,形成树枝状结构体,造成低电阻通路,破坏了电路板功能。非离子型污染物可穿透PC B 的绝缘层,在PCB板表层下生长枝晶。除了离子型和非离子型污染物,还有粒状污染物,例如焊料球、焊料槽内的浮点、灰尘、尘埃等,这些污染物会导致焊点质量降低、焊接时焊点拉尖、产生气孔、短路等等多种不良现象。

这么多污染物,到底哪些才是最备受关注的呢?助焊剂或锡膏普遍应用于回流焊和波峰焊工艺中,它们主要由溶剂、润湿剂、树脂、缓蚀剂和活化剂等多种成分,焊后必然存在热改性生成物,这些物质在所有污染物中的占据主导,从产品失效情况来而言,焊后残余物是影响产品质量最主要的影响因素,离子型残留物易引起电迁移使绝缘电阻下降,松香树脂残留物易吸附灰尘或杂质引发接触电阻增大,严重者导致开路失效,因此焊后必须进行严格的清洗,才能保障电路板的质量。

合明科技研发的水基清洗剂配合合适的清洗工艺能为芯片封装前提供洁净的界面条件。

合明科技运用自身原创的产品技术,满足芯片封装工艺制程清洗的高难度技术要求,打破国外厂商在行业中的垄断地位,为芯片封装材料全面国产自主提供强有力的支持。

推荐使用合明科技水基清洗剂产品。

合明科技致力于为SMT电子表面贴装清洗、功率电子器件清洗及先进封装清洗提供高品质、高技术、高价值的产品和服务。合明科技 (13691709838)Unibright 是一家集研发、生产、销售为一体的国家高新技术、专精特新企业,具有二十多年的水基清洗工艺解决方案服务经验,掌握电子制程环保水基清洗核心技术。水基技术产品覆盖从半导体芯片封测到 PCBA 组件终端的清洗应用。是IPC-CH-65B CN《清洗指导》标准的单位。合明科技全系列产品均为自主研发,具有深厚的技术开发能力,拥有五十多项知识产权、专利,是国内为数不多拥有完整的电子制程清洗产品链的公司。合明科技致力成为芯片、电子精密清洗剂的领先者。以国内自有品牌,以完善的服务体系,高效的经营管理机制、雄厚的技术研发实力和产品价格优势,为国内企业、机构提供更好的技术服务和更优质的产品。合明科技的定位不仅是精湛技术产品的提供商,另外更具价值的是能为客户提供可行的材料、工艺、设备综合解决方案,为客户解决各类高端精密电子、芯片封装制程清洗中的难题,理顺工艺,提高良率,成为客户可靠的帮手。

合明科技凭借精湛的产品技术水平受邀成为国际电子工业连接协会技术组主席单位,编写全球首部中文版《清洗指导》IPC标准(标准编号:IPC-CH-65B CN)(“Guidelines for Cleaning of Printed Boards and Assemblies”),IPC标准是全球电子行业优先选用标准,是集成电路材料产业技术创新联盟会员成员。

主营产品包括:集成电路与先进封装清洗材料、电子焊接助焊剂、电子环保清洗设备、电子辅料等。

半导体技术应用节点:FlipChip ;2D/2.5D/3D堆叠集成;COB绑定前清洗;晶圆级封装;高密度SIP焊后清洗;功率电子清洗。

上一篇:光电子集成芯片与3D堆叠封装技术应用分析及合明科···

下一篇:没有了!

![[x]](/template/default/picture/closeimgfz1.svg)