因为专业

所以领先

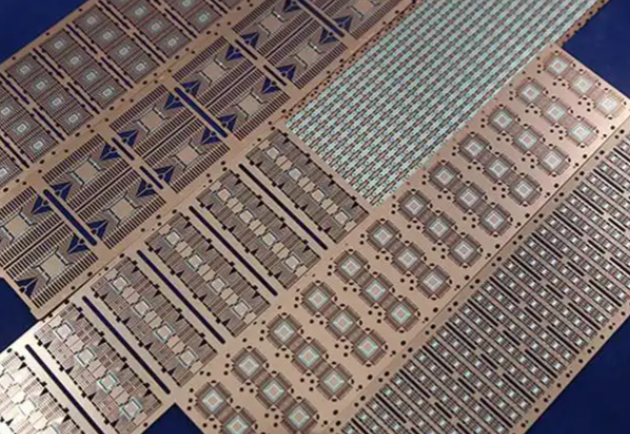

D2W(Die-to-Wafer)堆叠技术是3D先进封装的核心工艺之一,通过混合键合(Hybrid Bonding)实现芯片与晶圆的垂直堆叠,其技术特点如下:

无凸块互连:直接利用铜-铜(Cu-Cu)键合替代传统焊料凸块,消除寄生电容和电阻,实现超细间距(<10μm)和超高密度互连。

工艺流程:

晶圆预处理:对晶圆表面进行抛光、活化处理,形成SiO₂/SiCN介电层和铜焊盘。

芯片切割与转移:将已完成前端工艺的芯片切割并转移至载体晶圆。

对准与键合:通过高精度对准系统(如光学对准)将芯片与目标晶圆键合,利用范德华力和热处理形成共价键。

后道处理:完成RDL(再分布层)、TSV(硅通孔)等工艺,实现电气互联。

D2W技术凭借其高带宽、低延迟和高集成度优势,在多个领域实现突破性应用:

高性能计算(HPC):

处理器集成:AMD的MI300加速卡采用台积电SoIC技术,通过D2W堆叠实现CPU+GPU+HBM的异构集成,提升算力密度。

存储扩展:三星X-Cube技术将4颗SRAM堆叠在逻辑芯片上,通过TSV实现3D存储扩展,满足AI训练需求。

移动与消费电子:

图像传感器:索尼(Sony)和豪威(OmniVision)使用W2W混合键合生产CMOS图像传感器(CIS),但受限于I/O密度,主要面向中低端市场。

SoC封装:台积电InFO技术结合D2W工艺,应用于苹果A系列处理器,实现薄型化和高集成度。

汽车与工业电子:

传感器融合:通过D2W堆叠实现多传感器(如雷达、激光雷达)与MCU的集成,提升自动驾驶系统的实时性。

国际厂商主导:

台积电:SoIC技术覆盖WOW(晶圆堆叠)和COW(芯片堆叠),2023年月产能达2000片,目标2025年实现10μm以下凸点间距。

三星:X-Cube技术聚焦3D存储堆叠,2024年计划量产5nm节点的3D-SoC。

英特尔:Foveros Direct实现原子级键合,凸点间距缩至10μm,应用于Ponte Vecchio GPU。

国内厂商布局:

长电科技、通富微电等通过收购(如星科金朋)和自主研发,逐步突破D2W工艺,但良率与国际厂商仍有差距。

核心挑战:

工艺复杂度:D2W需晶圆厂级洁净环境(Class 1),颗粒控制(<1μm)和对准精度(<50nm)要求极高。

成本压力:设备投资(如深硅刻蚀机、键合机)高昂,单片成本是传统封装的3-5倍。

未来趋势:

异构集成深化:结合Chiplet设计,实现逻辑、存储、射频等异质芯片的混合键合。

本土化替代加速:国内政策支持(如“十四五”集成电路规划)推动设备(中微公司、北方华创)和材料(方邦股份)国产化。

D2W堆叠技术作为3D先进封装的前沿方向,正在重塑半导体产业格局。其市场应用从HPC向消费电子、汽车等领域扩展,但技术门槛和成本仍是规模化量产的瓶颈。未来,随着混合键合工艺的成熟和产业链协同创新,D2W有望成为Chiplet生态的核心支撑技术。

堆叠芯片清洗剂选择:

水基清洗的工艺和设备配置选择对清洗精密器件尤其重要,一旦选定,就会作为一个长期的使用和运行方式。水基清洗剂必须满足清洗、漂洗、干燥的全工艺流程。

污染物有多种,可归纳为离子型和非离子型两大类。离子型污染物接触到环境中的湿气,通电后发生电化学迁移,形成树枝状结构体,造成低电阻通路,破坏了电路板功能。非离子型污染物可穿透PC B 的绝缘层,在PCB板表层下生长枝晶。除了离子型和非离子型污染物,还有粒状污染物,例如焊料球、焊料槽内的浮点、灰尘、尘埃等,这些污染物会导致焊点质量降低、焊接时焊点拉尖、产生气孔、短路等等多种不良现象。

这么多污染物,到底哪些才是最备受关注的呢?助焊剂或锡膏普遍应用于回流焊和波峰焊工艺中,它们主要由溶剂、润湿剂、树脂、缓蚀剂和活化剂等多种成分,焊后必然存在热改性生成物,这些物质在所有污染物中的占据主导,从产品失效情况来而言,焊后残余物是影响产品质量最主要的影响因素,离子型残留物易引起电迁移使绝缘电阻下降,松香树脂残留物易吸附灰尘或杂质引发接触电阻增大,严重者导致开路失效,因此焊后必须进行严格的清洗,才能保障电路板的质量。

合明科技研发的水基清洗剂配合合适的清洗工艺能为芯片封装前提供洁净的界面条件。

合明科技运用自身原创的产品技术,满足芯片封装工艺制程清洗的高难度技术要求,打破国外厂商在行业中的垄断地位,为芯片封装材料全面国产自主提供强有力的支持。

推荐使用合明科技水基清洗剂产品。

![[x]](/template/default/picture/closeimgfz1.svg)